本文共 2587 字,大约阅读时间需要 8 分钟。

声明:为方便自己学习,以及知识的完整性,将师兄的博客文章转载到这里!

FPGA由6部分组成,分别为可编程输入/输出单元(IOB)、基本可编程逻辑单元(SLENCE)、嵌入式块RAM(block ram)、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

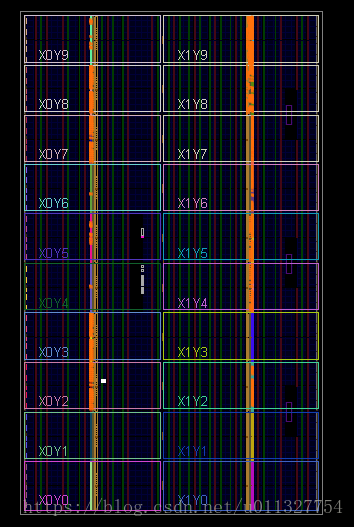

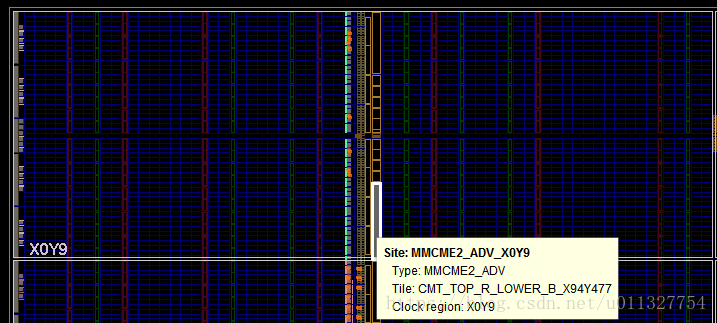

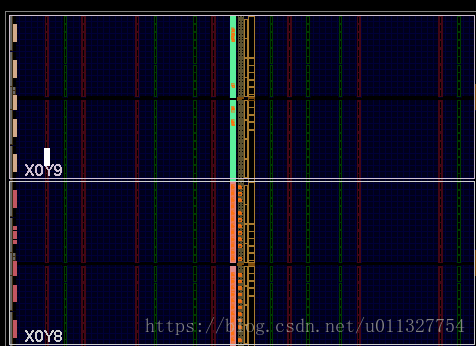

整个FPGA的资源分布图如下:

上图的分块按照时钟域分的块,前面有文章介绍FPGA的时钟中有详细介绍分块的规则。

------------------------------------------------------------------------------------------------------

1)IOB可编程输入输出单元:

大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

---------------------------------------------------------------------------------------------------------

基本可编程逻辑单元(CLB)

如上图所示,左边SLICE为SLICEM,右边为SLICEL。

CLB内部的两个Slice是相互独立的,各自分别连接开关阵列(Switch Matrix),以便与通用布线阵列(General routing Matrix)相连。

在Xilinx FPGA设计工具中,Slice的位置用“XmYn”表示,其中m为Slice所在横坐标,一个CLB的两个Slice的横坐标分别是m和m+1;n为CLB的纵坐标,一个CLB的两个Slice有相同的n。Virtex-5左下角的Slice编号为X0Y0。

实际上,查找表类似于一个ROM(印象中是SRAM),容量是64bit,6个输入作为地址输入,存储的内容作为布尔运算的结果。查找表中的内容由开发环境生成并在FPGA配置时加载进去。(每个SLICE有4个查找表在SLICE的左边)。Slice中的触发器可以配置成多种工作方式,例如是FF或Latch,同步复位或异步复位、复位高有效或低有效等。(每个SLICE有8个寄存器,在SLICE的最右端)CLB内部包含多个选择器。CLB的选择器与一般的选择器不同,它们没有选择端。通路的选择在FPGA配置后固定下来。(上图中每个SLICE有3个二选一选择器)CLB内部还包含了一个重要的资源——进位链,其作用是方便加法器的实现。(每个SLICE有一个四进位链CARRY4)

SLICEM的结构与SLICEL的结构类似,最大的区别是使用了一个新的单元代替SLICE中的查找表(如下图示)。这个新的单元可以配置为LUT、RAM、ROM或移位寄存器(SRL16/SRL32),从而可以实现LUT的逻辑功能,也能做存储单元(多个单元组合起来可以提供更大的容量)和移位寄存器(提供延迟等功能),其中SLICEM中LUT的输入端读地址和写地址为8位,高两位可能是将4个LUT并联一起作为一个大的RAM或ROM时用,同时SLICEL和SLICEM的LUT均可设为5位查找表或6位查找表。

CLB内部查找表、触发器、多路器等基本单元的配置是由ISE自动完成,一般情况下不需要设计者干预。但是,如果认为有必要,设计者可以通过ISE中集成的FPGA底层编辑器——FPGA Editor直接编辑CLB内部触发器和多路器的配置。

-------------------------------------------------------------------------------------------------------------------

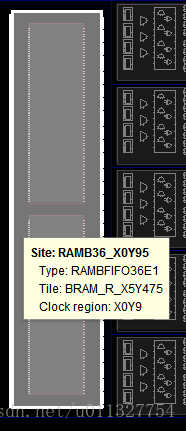

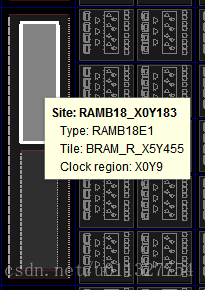

BLOCK RAM:

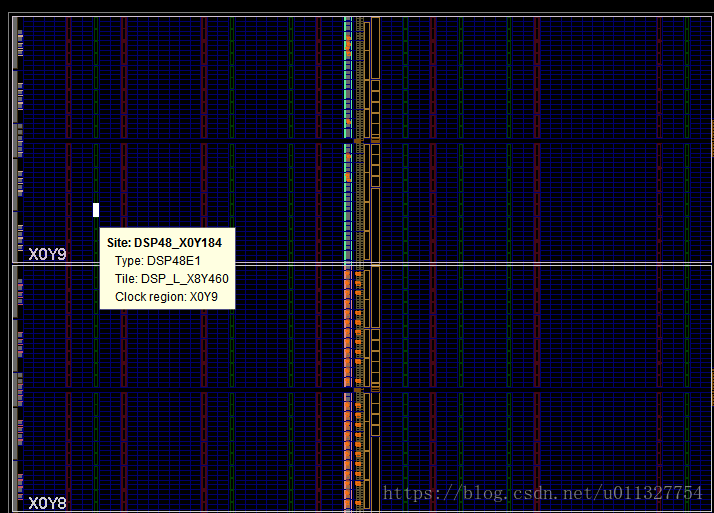

()

如上图所示,block ram所处的那一列位置全是36BLOCK RAM ,其中每个block RAM中又分为上下两块,上半部分为18RAMB下半部分为FIFO18。在FIFO例化的时候可以将BLOCK RAM设置为FIFO,不会使用额外的CLB资源,并且这部分RAM是真双口RAM。

-------------------------------------------------------------------------------

上图所示中的一列全是DSP48,为FPGA内部模块。

有4个输入,分别是A、B、C、D。一个输出P。从输入得到输出,我们用一个函数公式表达:P=(D±A)*B±C。请把这个公式背下来,之后的变形使用也靠它了。这里面A是30bit,B是18bit,C是48bit,D是25bit。(D±A)出来是25bit,乘法就是25*18bit。P是48bit。

这个式子就是dsp48e1的功能简介了。当然里面有更多的东西需要去配置和实现,但主体框架就是这个。我们用它来实现乘法加法这些东西。

如果你直接使用dsp48的ip,通过简单的公式选择,动动鼠标就可以配置好公式。也可以直接用原语调用。这里就不介绍这个了。详见:https://blog.csdn.net/kebu12345678/article/details/54973854

--------------------------------------------------------------------

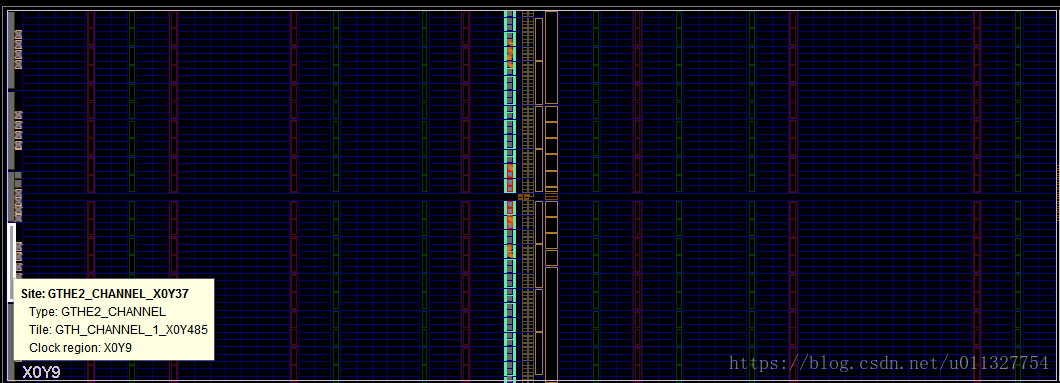

GTH固核:

GTH在该时钟块的一侧,旁边为GTH的4个PAD(输入输出的差分引脚),一列全是GTH固核。中间输入多出的两个PAD为该GTH块的参考时钟引脚。这就是4路GTH一个块指的是在同一个时钟块中的四个GTH固核。关于GTH见前几篇文章。

-------------------------------------------------------------------------------------------

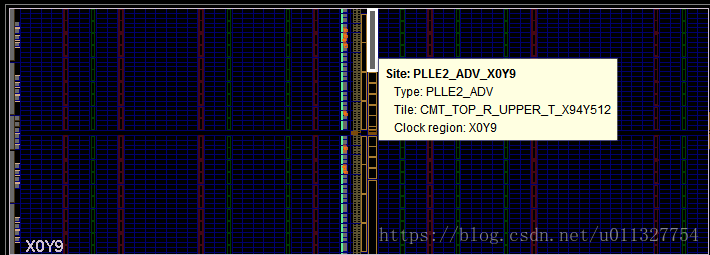

上图所示两个模块为该时钟块的时钟管理模块(PLL和MMCM)。

------------------------------------------------------

剩下的一些模块暂时不多做介绍,基本都集中在时钟块中间一列。

原文地址: